Z, finding all floating-unknown signals 2.6-29, C-45 **zero** 1.2-4, 1.2-6

| utgrp SIMIC primitive A-65                              | wired-or (1-dominance) 2.7-22                              |

|---------------------------------------------------------|------------------------------------------------------------|

|                                                         | wire-tie dominance 2.7-22                                  |

|                                                         | <b>0, 1, X</b> 2.7-23                                      |

| vector aliases 2.4-4, 2.4-8, C-2, C-26                  | wire-tie, conflict (X-dominance) 2.7-22                    |

| vector range 1.2-13, B-2                                | wire-ties, creating 2.7-22                                 |

| vectors 1.2-13, B-2                                     | wiring delays 2.2-6, C-41                                  |

| version number 1.1-1                                    | write                                                      |

|                                                         | <b>begin</b> 2.4-6, C-75                                   |

|                                                         | <b>change</b> 2.4-6, C-75                                  |

| w, width (SNL keyword) 2.7-29, B-18                     | <b>expand</b> 2.4-5, C-75                                  |

| warn                                                    | file 2.1-2, 2.4-2, C-73                                    |

| <pre><timing-check-name> C-70</timing-check-name></pre> | header 2.4-5, C-76                                         |

| conflict C-71                                           | list 2.4-2, 2.4-3, C-73                                    |

| file C-71                                               | <b>prange</b> 2.4-7, 2.6-16, C-73                          |

| hazard C-69                                             | pstep 2.4-6, 2.5-3, C-74                                   |

| memlatch C-68                                           | tnum 2.4-5, C-76                                           |

| memspike C-69                                           | tstep 2.4-6, C-74                                          |

| near C-69                                               | value 2.4-8, C-74                                          |

| oscillation C-71                                        | write options (see print/write)                            |

| part C-70                                               | 1 1 /                                                      |

| prange C-68                                             |                                                            |

| pulse C-70                                              | X (stimulus symbol) 2.3-11                                 |

| spike C-70                                              | X address lines                                            |

| stop 2.6-24, C-71                                       | at <b>rama</b> A-48                                        |

| <b>strobe</b> 2.8-8, C-70                               | at <b>ramb</b> A-50                                        |

| term C-71                                               | at <b>ramc</b> A-52                                        |

| unstable C-70                                           | at <b>rom</b> A-54                                         |

| <b>x</b> C-69                                           | threshold C-24                                             |

| warn command                                            | X, finding all unknown signals 2.6-29, C-45                |

| (also, see <b>break</b> ) 2.6-23                        | xpropagate                                                 |

| and break option differences 2.6-24                     | <timing-check-name> 2.6-36, C-77, C-78</timing-check-name> |

| defaults 2.6-24, C-68                                   | <b>filter</b> 2.6-37, C-78                                 |

| syntax C-68 – C-72                                      | liberal 2.6-37, C-78                                       |

| warning messages                                        | list 2.6-37, C-78                                          |

| directing C-71                                          | near 2.5-2, 2.6-36, C-77                                   |

| format 2.6-23                                           | part 2.6-36, C-77, C-78                                    |

| suppressing excessive messages 2.6-24,                  | <b>spike</b> 2.5-3, 2.6-10, 2.6-35, 2.7-21, C-77           |

| C-71                                                    | X-propagation, disabling 2.6-35, C-77                      |

| waveforms 2.3-1, 2.3-2                                  | X-propagation, enabling 2.6-35, C-77                       |

| whitespace 1.1-9, 1.2-1                                 | X-pulse creation/propagation 2.5-2, 2.5-3                  |

| width (stimulus) 2.3-3, C-25                            |                                                            |

| width, and stimulus radix 2.3-13                        |                                                            |

| wildcard, in signal names 2.4-4, 2.9-4, 2.9-5,          | Z (stimulus symbol) 2.3-12                                 |

| 2.9-6, C-2                                              | Z threshold, tester interface file 2.8-11, C-64            |

| window strobe (SW) 2.8-8, C-28                          | C-65                                                       |

| wired-and (0-dominance) 2.7-22                          | Z, at gate inputs 2.7-16                                   |

|                                                         |                                                            |

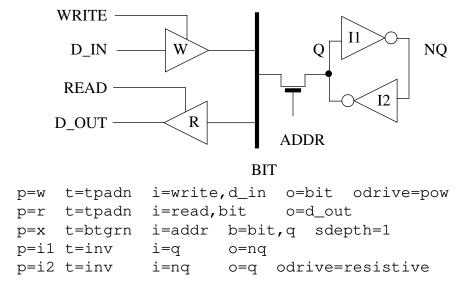

| and X-propagation 2.6-35, 2.8-9               | tpadn SIMIC primitive A-60                       |

|-----------------------------------------------|--------------------------------------------------|

| tgate SIMIC primitive A-57                    | tpadp SIMIC primitive A-61                       |

| tgen                                          | tpcf SIMIC primitive A-62, A-63                  |

| disconnect 2.8-10, C-64                       | trace                                            |

| file 2.8-9, C-64                              | <b>begin</b> 2.6-26, C-66                        |

| hiz 2.8-11, C-64, C-65                        | <b>expand</b> 2.6-12, 2.6-25, C-66               |

| target 2.8-9, C-64                            | file 2.6-25, C-67                                |

| time field (print/write) 1.1-8                | list 2.6-12, 2.6-15, 2.6-26, C-66                |

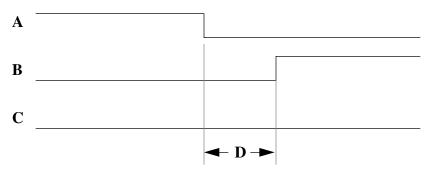

| time-based inputs (waveforms) 2.3-1           | prange 2.6-25, C-66                              |

| time-set switching 2.3-2                      | term 2.6-25, C-67                                |

| time-set, default 2.8-7                       | trace activity 2.6-12                            |

| time-sets, defining $2.8-3-2.8-7$             | trace messages, format 2.6-25                    |

| time-stamp (write) 2.4-1                      | trace, and slowest paths 2.6-26                  |

| time-units 2.7-7                              | trace, removing 2.6-15                           |

| time-units keyword 2.7-7, B-6                 | trace, show causality 2.6-12                     |

| time-units, and real-time 2.7-7, B-6          | tracing circuit activity 2.6-24 – 2.6-26, C-66   |

| timing check parameters, querying 2.6-37,     | trans, transistors (SNL keyword) 2.7-29,         |

| C-50                                          | B-18                                             |

| timing check parameters, run-time modifica-   | tristating outputs, fault detection for 57, C-37 |

| tion 2.6-38, C-62                             | troubleshooting design problems $2.6-1-2.6-41$   |

| timing checks, and X-propagation 2.6-36, C-77 | true-value simulation 2.5-2                      |

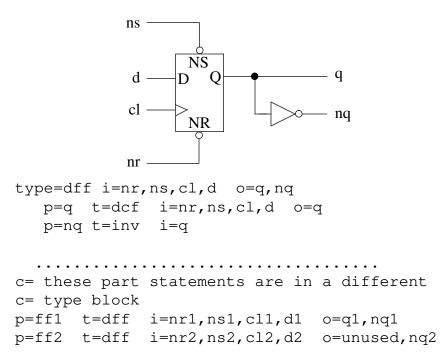

| timing checks, functional 2.7-17, 2.7-18      | type block 1.2-4, 1.2-5, 2.7-1, B-8              |

| timing generators 2.3-1, 2.3-2                | type name 1.2-4                                  |

| associating with inputs 2.8-7                 | type names, and search order 2.7-29              |

| default 2.8-7                                 | type statement 1.1-4, 1.2-1, 1.2-4, 2.7-1, B-8   |

| drive masks 2.8-2                             | <b>typical</b> timing 2.2-6, 2.6-33, C-41        |

| enable masks 2.8-2                            |                                                  |

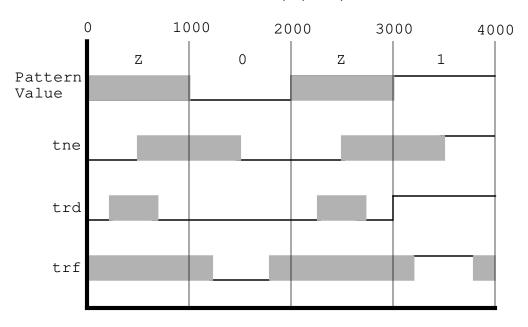

| NE enable mask 2.8-2, 2.8-5, C-27             |                                                  |

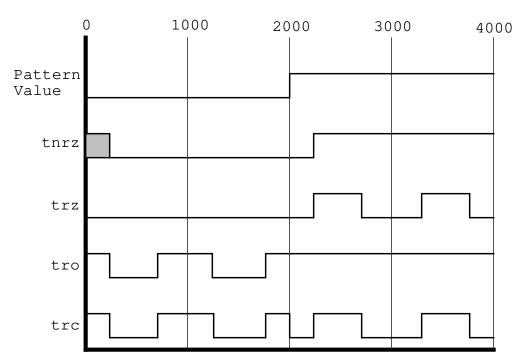

| NRZ drive mask 2.8-2, 2.8-4, C-27             | underscore, specifying auto-numbering 24, 40,    |

| RC drive mask 2.8-2, 2.8-4, C-27              | 41                                               |

| RD enable mask 2.8-3, 2.8-5, C-27             | undetectable faults 9                            |

| RF enable mask 2.8-3, 2.8-5, C-27             | undetected faults                                |

| RO drive mask 2.8-2, 2.8-4, C-27              | file                                             |

| RZ drive mask 2.8-2, 2.8-4, C-27              | generating 33                                    |

| suppressing marks 2.8-5                       | using iteratively 26, 39 – 41                    |

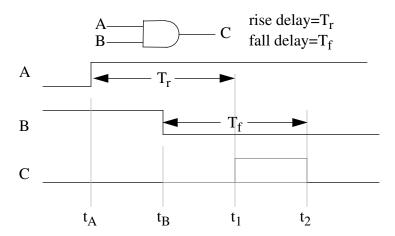

| timing hazards, combinational 2.6-2           | reporting 35, C-32                               |

| timing set, <b>typical</b> default 2.6-33     | unsensitized faults                              |

| timing sets, loading 2.6-33                   | file                                             |

| timing table selection 2.2-6, C-41            | generating 13, C-56                              |

| timing-checks (SNL keyword) 2.6-4, 2.7-17,    | using in fault simulation 62                     |

| 2.7-18, B-18                                  | reporting 17, 21, 22, C-57                       |

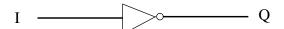

| tinvn SIMIC primitive A-58                    | unused (SNL reserved name) 2.7-27                |

| tinvp SIMIC primitive A-59                    | <b>unused</b> pins 1.2-4, 2.7-27                 |

| tncf (tcf) SIMIC primitive A-55, A-56         | user-defined primitives                          |

| tolerance, (SNL keyword) B-3, B-4             | see boolean element                              |

| topological checks 2.2-1                      | utgrn SIMIC primitive A-64                       |

| SIMIC primitives 1.2-7                         | specifying confidence level 58, 59, C-36           |

|------------------------------------------------|----------------------------------------------------|

| <b>simulate</b> 1.1-7, C-63                    | specifying sample size 57, 58, C-36                |

| prange C-63                                    | sticky parameters 1.1-10, 2.6-17                   |

| simulate-till-stable (patterns) 2.3-1          | stimulus default duration 2.3-3, 2.3-14, C-25      |

| simulation output format 1.1-8, 2.4-1          | stimulus default format 2.3-3, C-25                |

| simulation, initiating C-63                    | stimulus default strength 2.3-3, 2.3-9, C-25       |

| single quotes 1.2-3                            | stimulus definition $2.3-1-2.3-16$                 |

| single-stuck fault model 7                     | stimulus hierarchy 2.3-8                           |

| size metrics, totalled                         | stimulus name 2.3-3, C-25                          |

| cell widths 2.2-1, 2.7-29, B-9                 | stimulus selection 2.3-5                           |

| pads 2.2-1, 2.7-29, B-9                        | stimulus width 2.3-3, C-25                         |

| transistors 2.2-1, 2.7-29, B-9                 | stimulus-input association 1.1-7, 2.3-5            |

| skewing stimuli 2.3-5                          | strength and depth correspondences 2.6-5,          |

| skip <b>!format</b> field 1.2-12, B-7          | C-24                                               |

| SNL hierarchical precedence 2.7-25 – 2.7-27    | strengths (print/write) 2.4-8, C-47, C-74          |

| SNL keywords                                   | strobe error 2.6-23, 2.8-8                         |

| categories B-9                                 | strobes                                            |

| valid values for B-12                          | associating with inputs 2.8-8, 2.8-9               |

| SNL statements and keywords B-1 – B-18         | default point strobe 2.8-9                         |

| SOFT potential detection option 44, C-33       | defining 2.8-8, C-28                               |

| SP point strobe 2.8-8, C-28                    | point strobe (SP) 2.8-8, C-28                      |

| spacing signals (print/write) 1.1-7            | window strobe (SW) 2.8-8, C-28                     |

| specifying signal names                        | strobing, time of 27                               |

| factored names 2.4-4, C-2                      | suppressed faults 42, 43                           |

| formatted for print/write 1.1-7, 2.4-2, 2.4-3, | reporting 21, 34, C-32, C-57                       |

| C-46, C-73                                     | switch-level 56, C-37                              |

| meta-words 2.4-4, C-1                          | suppressed faults report, example 43               |

| using part names 2.4-4, C-2                    | suppressed spike message 2.6-10, 2.6-24            |

| vector aliases 2.4-4, C-2                      | SW window strobe 2.8-8, C-28                       |

| wildcard 2.4-4, 2.9-4, 2.9-5, 2.9-6, C-2       | switch-level depth 2.7-24                          |

| spike control parameters, querying 2.6-36,     | switch-level faults, including 56, C-37            |

| C-51                                           | symbols (combined level/strength) 2.3-10           |

| spike control parameters, run-time modifica-   | symbols listing file option 2.2-5, C-40            |

| tion 2.6-37, C-78                              |                                                    |

| spike filter mode 2.5-3, 2.6-10                |                                                    |

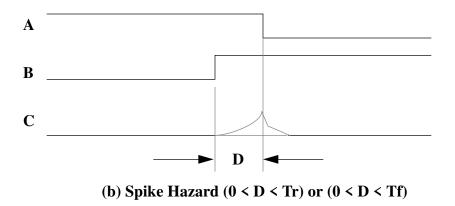

| spike hazard 2.5-3, 2.6-2, 2.7-19              | <b>t, type</b> (SNL keyword) 1.2-4, 1.2-5, 1.2-11, |

| spike messages suppressed 2.6-10, 2.6-24       | B-18                                               |

| spike propagation control (SNL) 2.7-19 -       | target tester, specifying 2.8-9, C-64              |

| 2.7-21                                         | tcf (tncf) SIMIC primitive A-55, A-56              |

| spike propagation mode 2.5-3                   | terminal output 1.1-7                              |

| stability, and decays 2.5-3, C-24              | test emulation mode, initiating 2.8-1              |

| state (SNL keyword) A-9, A-12, B-17            | test field (print/write) 1.1-8                     |

| static (ON ideal switches) 2.5-4, C-23         | test number 2.3-2                                  |

| static delays (ON ideal switches) 2.5-4, C-23  | test period (see period)                           |

| static logic, and charge decay 2.5-4           | tester emulation 2.3-1, 2.8-1 – 2.8-9, C-26        |

| statistical fault simulation 57 – 61, C-36     | tester interface file 2.8-9 – 2.8-13, C-64         |

| retrieving previously-compiled description   | rfile 17, C-57                                                  |

|----------------------------------------------|-----------------------------------------------------------------|

| 2.2-6, C-40                                  | <b>ufile</b> 13, C-56                                           |

| return-to-complement (RC) 2.8-2, 2.8-4, C-27 | sensitized faults                                               |

| return-to-drive (RD) 2.8-3, 2.8-5, C-27      | reporting 17, 21, 22, C-57                                      |

| return-to-float (RF) 2.8-3, 2.8-5, C-27      | series depth, specifying 2.7-24                                 |

| return-to-one (RO) 2.8-2, 2.8-4, C-27        | set                                                             |

| return-to-zero (RZ) 2.8-2, 2.8-4, C-27       | <pre><timing-check-name> 2.6-38, C-62</timing-check-name></pre> |

| RF enable mask 2.8-3, 2.8-5, C-27            | <b>change</b> 2.6-15, 2.6-33, 2.7-14, C-61                      |

| rise (SNL keyword) 2.7-9, B-5                | <b>decay</b> 2.6-35, 2.7-15, 2.7-16, C-61                       |

| rom SIMIC primitive A-53, A-54               | <b>fall</b> 2.6-33, 2.7-14, C-61                                |

| initializing A-54                            | <b>hiz</b> 2.6-30, C-60                                         |

| X address lines A-54                         | <b>list</b> 2.6-15, 2.6-33, 2.6-35, 2.7-14, 2.7-16,             |

| root name 1.2-13, B-2                        | C-61                                                            |

| representing declared array 1.2-13           | <b>list</b> (with <b>no</b> prefix) 2.6-31, C-60                |

| run files 1.1-12                             | one 2.6-30, C-60                                                |

| RZ drive mask 2.8-2, 2.8-4, C-27             | part 2.6-38, C-62                                               |

|                                              | <b>rise</b> 2.6-33, 2.7-14, C-61                                |

|                                              | <b>tnum</b> 2.6-30, C-60                                        |

| <b>-s</b> command line option 1.1-1, 2.1-2   | <b>x</b> 2.6-30, C-60                                           |

| sample, fault 57 – 61, C-36                  | <b>zero</b> 2.6-30, C-60                                        |

| save                                         | set drive                                                       |

| file 2.6-40, C-55                            | set ldrive                                                      |

| <b>prange</b> 2.6-40, C-55                   | set hdrive 2.6-39                                               |

| <b>pstep</b> 2.6-40                          | setting breakpoints 2.6-18 – 2.6-23                             |

| save circuit state 2.6-40                    | setup time checks                                               |

| saving circuit state C-55                    | <b>setup</b> (all setup checks) 2.6-5, 2.7-18,                  |

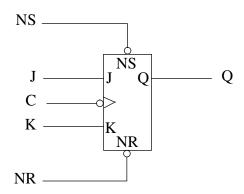

| saving compiled description 2.2-4, C-40      | A-20, A-22, A-24, A-26, A-31,                                   |

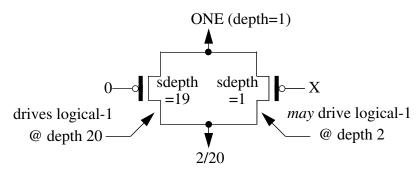

| sdepth, series-depth (SNL keyword) 2.7-24,   | A-33, A-56, A-63                                                |

| B-17                                         | <b>setup.d</b> 2.6-5, 2.7-17, A-20, A-22, A-24,                 |

| default value A-18                           | A-26                                                            |

| search order for type names 2.7-29           | <b>setup.j</b> 2.6-4, 2.6-5, 2.7-17, 2.7-18, A-31,              |

| seed, random number generator 58, C-36       | A-33                                                            |

| selecting faults 25 – 27, C-30               | <b>setup.k</b> 2.6-5, 2.7-18, A-31, A-33                        |

| sensitization analysis 7                     | setup.nr 2.6-4, 2.6-5, 2.7-17, 2.7-18, A-20,                    |

| box score 16, 17                             | A-22, A-24, A-26, A-31, A-33,                                   |

| description of 7, 8, 11, 12                  | A-56, A-63                                                      |

| directing SIMIC to perform 13, C-56          | setup.ns 2.6-4, 2.6-5, 2.7-17, 2.7-18, A-20,                    |

| local nature of 11                           | A-22, A-24, A-26, A-31, A-33,                                   |

| supported elements 13                        | A-56, A-63                                                      |

| using in fault simulation $62 - 64$ , C-34   | signal arrays 1.2-13, B-2                                       |

| vs. fault simulation 12                      | signal header (print/write) 1.1-7, 2.4-1                        |

| sensitize                                    | signal loading, querying 2.6-35, C-50                           |

| directory 23, 24, C-58, C-59                 | signal name (hierarchical) 2.7-4                                |

| <b>expand</b> 22, C-58                       | signal names, specifying 2.4-4, C-1                             |

| <b>list</b> 13, C-56                         | SIMIC Network Language (SNL) 1.1-3, 1.1-4                       |

| report 18, C-58                              | 1.2-1 - 1.2-17, $2.7-1 - 2.7-30$                                |

| 2.6-28, C-44, C-45                                | X address lines A-50                                  |

|---------------------------------------------------|-------------------------------------------------------|

| probing, displaying signal loads 2.6-28, C-45     | ramc SIMIC primitive A-51, A-52                       |

| progress reports 66, 67, C-38                     | initializing A-52, C-21                               |

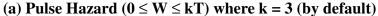

| pulse hazard 2.6-2                                | X address lines A-52                                  |

| pulse hazard, defining width of 2.6-2, C-24       | random fault samples 57 – 61, C-36                    |

| pulse-extended period 2.8-3                       | random number generator seed 58, C-36                 |

| pulse-width checks                                | RC drive mask 2.8-2, 2.8-4, C-27                      |

| <b>pw</b> (all pulse-width checks) 2.6-5, 2.7-18, | RD enable mask 2.8-3, 2.8-5, C-27                     |

| A-20, A-22, A-24, A-26, A-31,                     | reference time 1.1-8                                  |

| A-33, A-56, A-63                                  | referenced type 1.2-5                                 |

| <b>pw.c.h</b> 2.6-4, 2.7-17, A-20, A-22, A-24,    | referencing global delays 2.7-9, B-6                  |

| A-26, A-31, A-33, A-56                            | remarks (run commands) C-1                            |

| <b>pw.c.l</b> 2.6-4, 2.7-17, A-20, A-22, A-24,    | repetitive sequences 2.3-7                            |

| A-26, A-31, A-33, A-56, A-63                      | replay simulation 2.6-40, 2.6-41                      |

| pw.nr 2.6-4, 2.7-17, A-20, A-22, A-24,            | report                                                |

| A-26, A-31, A-33, A-56, A-63                      | collapsed faults only 36, C-32                        |

| <b>pw.ns</b> 2.6-4, 2.7-17, A-20, A-22, A-24,     | detected faults 34, 35, C-32                          |

| A-26, A-31, A-33, A-56, A-63                      | equivalent faults 17, 18, 19, 20, 34, C-32, C-57      |

|                                                   | progress 66, 67, C-38                                 |

| query                                             | sensitized faults 17, 21, 22, C-57                    |

| <b>?check part</b> 2.6-37, C-50                   | suppressed faults 21, 34, C-32, C-57                  |

| <b>?clamp</b> 2.6-32                              | undetected faults 35, C-32                            |

| <b>?decay list</b> 2.6-34, C-50                   | unsensitized faults 17, 21, 22, C-57                  |

| <b>?define</b> 2.5-1, C-50                        | width of lines 22, 36, C-33, C-58                     |

| <b>?delay list</b> 2.6-32, C-50                   | reserved names (one,unused,zero) 1.2-4                |

| ?drive list                                       | resimulate hazard 2.6-12, 2.6-15                      |

| drive parameters, query 2.6-39                    | resimulation 2.6-40, 2.6-41                           |

| <b>?loading list</b> 2.6-35, C-50                 | resistive (drive strength) 2.7-24, B-13, B-14         |

| <b>?print</b> 2.4-9, C-51                         | B-16                                                  |

| <b>?set</b> 2.6-32                                | resistive (stimulus strength) 2.3-4, 2.3-9, C-25      |

| <b>?spike list</b> 2.6-36, C-51                   | resistive strength, mapping to depth 2.6-6            |

| <b>?write</b> 2.4-9, C-51                         | RESOLVE potential detection option 44, 45             |

| file 2.6-18                                       | 47, 50, 51, C-33                                      |

| quit 1.1-2, 1.1-8, C-52                           | response time, and patterns 2.3-2                     |

| quotes 1.2-3, 2.1-2                               | restore                                               |

|                                                   | file 2.6-40, C-53                                     |

|                                                   | <b>prange</b> 2.6-41, C-54                            |

| r, rem, remark (SNL keyword) 1.2-15, B-1,         | <b>tnum</b> 2.6-12, 2.6-15, 2.6-39, 2.6-41, C-53      |

| B-2, B-17                                         | restore circuit state 2.6-39                          |

| radix escapes (stimuli) 2.3-12                    | from checkpoint file 2.6-39, 2.6-41, C-53             |

| rama SIMIC primitive A-47, A-48                   | to initially unknown state C-53                       |

| initializing A-48, C-21                           | to last stable point 2.6-12, 2.6-39, 2.6-40,          |

| X address lines A-48                              | C-53                                                  |

| ramb SIMIC primitive A-49, A-50                   | restricting command intervals ( <b>prange</b> ) 2.4-7 |

| initializing A-50, C-21                           | 2.6-16                                                |

| options banner (print/write) 1.1-7, 2.4-1, 2.5-1 | previously-compiled description 2.2-6, C-40     |

|--------------------------------------------------|-------------------------------------------------|

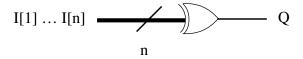

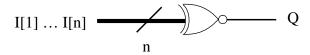

| or SIMIC primitive A-41                          | primary input grouping (stimuli) 2.3-7          |

| orise, output-rise (SNL keyword) 2.7-11,         | primary inputs 2.3-1                            |

| B-17                                             | <b>primitive</b> (SNL composition) 2.7-28, B-15 |

| oscillating signals, set to X 2.6-5, C-23        | primitive values (stimuli) 2.3-9                |

| oscillation check, disabling 2.6-5, C-24         | primitives 1.2-7, A-1 – A-65                    |

| oscillation, definition of 2.6-5, C-23           | primitives, user-defined                        |

| output list 1.2-4, 1.2-5                         | see <b>boolean</b> element                      |

| output sensing, time of 27                       | print                                           |

|                                                  | <b>begin</b> 2.4-6, C-48                        |

|                                                  | <b>change</b> 2.4-6, C-48                       |

| <b>p, part</b> (SNL keyword) 1.2-5, 1.2-11, B-17 | <b>expand</b> 2.4-5, C-48                       |

| <b>pads</b> (SNL keyword) 2.7-29, B-17           | header 2.4-5, C-48                              |

| paralleled elements 2.2-1, 2.7-13                | <b>list</b> 1.1-7, 2.4-2, 2.4-3, C-46           |

| part name 1.2-5                                  | <b>prange</b> 2.4-7, 2.6-16, C-46               |

| part name (hierarchical) 2.7-4                   | <b>pstep</b> 2.4-6, 2.5-3, C-47                 |

| part statement 1.1-4, 1.2-1, 1.2-5, 2.7-1, B-9   | <b>tnum</b> 2.4-5, C-49                         |

| patterns 1.1-6, 2.3-1                            | tstep 2.4-6, C-47                               |

| patterns, and test emulation mode 2.8-2          | <b>value</b> 2.4-8, C-47                        |

| period                                           | print/write                                     |

| changing during simulation 2.8-1, C-12           | all signals 2.4-3, C-46, C-74                   |

| defining 2.8-1                                   | array radix 2.7-5                               |

| pulse-extended 2.8-3                             | cancel all signals 2.4-4                        |

| physical size metrics 2.7-29                     | character set 2.4-7                             |

| pin loading, specifying 2.7-11                   | column width 2.4-4, C-48, C-75                  |

| pin names, referencing (SNL) A-1, A-2            | format (#) 2.4-3, C-46, C-73                    |

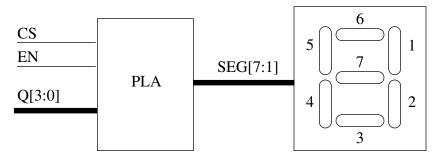

| <b>pla</b> SIMIC primitive A-42 – A-46           | format (*) 1.1-7, 2.4-3, C-46, C-73             |

| defining functionality A-43 – A-46, C-20         | on activity 2.4-6, C-48, C-75                   |

| placeholder comma 2.7-9                          | options banner 1.1-7, 2.4-1, 2.5-1              |

| placeholder hyphen 1.2-12, B-7                   | periodically (over time) 2.4-6, C-47, C-74      |

| point strobe (SP) 2.8-8, C-28                    | periodically (stable-states) 2.4-5, 2.5-3,      |

| posint, posinteger (positive integer format)     | C-47, C-74                                      |

| 1.2-13, 2.4-8, B-3, B-4, C-26                    | restricting active interval 2.4-7, 2.6-16       |

| positioning precedence (stimuli) 2.3-16          | signal header 2.4-1                             |

| postdecay (stability) 2.5-4, C-24                | specifying offset 2.4-6, C-48, C-75             |

| potential detections                             | specifying signals 2.4-2, 2.4-3, C-46, C-73     |

| definition of 8                                  | suppressing header 2.4-5, C-48, C-76            |

| handling 44 – 51, C-33                           | suppressing strengths 2.4-7, C-47, C-74         |

| NONE option 44, 45, 47, 48, 49, C-33             | suppressing test number 2.4-5, C-48, C-76       |

| RESOLVE option 44, 45, 47, 50, 51, C-33          | print/write output format 1.1-8, 2.4-1          |

| SOFT option 44, C-33                             | probing all signals 2.6-29, C-44                |

| power (drive strength) 2.7-24, B-13, B-14,       | probing signal values 2.6-27 – 2.6-29, C-44     |

| B-16                                             | C-45                                            |

| power (stimulus strength) 2.3-4, 2.3-9, C-25     | probing wire-ties, and displaying drivers       |

| <b>prange</b> keyword 2.6-16, 2.6-17, C-2        | 2.6-28                                          |

| <b>predecay</b> (stability) 2.5-4                | probing, and displaying element inputs 2.6-27   |

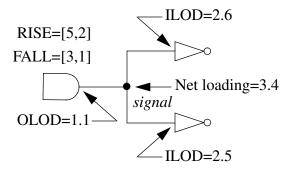

| loading at signals, querying 2.6-35, C-50            | net loading, specifying 2.7-12, A-34                  |

|------------------------------------------------------|-------------------------------------------------------|

| loading timing sets 2.6-33                           | network description file 1.2-1                        |

| loading, net 2.7-12, A-34                            | <b>no</b> (command prefix) 1.1-10                     |

| loading, pin 2.7-11                                  | no-envelope (NE) 2.8-2, 2.8-5, C-27                   |

| local delays 2.7-11                                  | <b>noname</b> (unspecified default file) 1.1-6, 2.1-3 |

| logical-0 ( <b>zero</b> ) 1.2-4, 1.2-6               | NONE potential detection option 44, 45, 47            |

| logical-1 ( <b>one</b> ) 1.2-4, 1.2-6                | 48, C-33                                              |

| look                                                 | non-return-to-zero (NRZ) 2.8-2, 2.8-4, C-27           |

| hiz 2.6-29, C-45                                     | nor SIMIC primitive A-38                              |

| <b>inputs</b> 2.6-27, C-44                           | norl SIMIC primitive A-39                             |

| list 2.6-27, C-44                                    | NRZ drive mask 2.8-2, 2.8-4, C-27                     |

| outputs 2.6-28, C-45                                 | , , , , , , , , , , , , , , , , , , , ,               |

| x 2.6-29, C-45                                       |                                                       |

| look expand 2.6-29                                   | o, onet, output-nets (SNL keyword) 1.2-5              |

| look message, format 2.6-27                          | 1.2-11, B-15                                          |

|                                                      | o, opin, output-pins (SNL keyword) 1.2-4              |

|                                                      | 1.2-11                                                |

| macro (SNL composition) 2.7-28, B-15                 | ochange, output-change (SNL keyword)                  |

| macro definition 1.2-4, 2.7-3                        | 2.6-8, 2.7-11, B-15                                   |

| macro, instantiating 2.7-3                           | oct, octal (array format) 1.2-13, B-3                 |

| main type 2.2-2, 2.3-1, 2.7-4                        | oct, octal (output format) 2.4-8, C-26                |

| marks, suppressing 2.8-5                             | <b>octal</b> (stimulus format) 2.3-4, 2.3-11, C-25    |

| master period (see period)                           | odec, output-decay (SNL keyword) 2.7-15               |

| <b>maximum</b> timing 2.2-6, 2.6-33, C-41            | B-16                                                  |

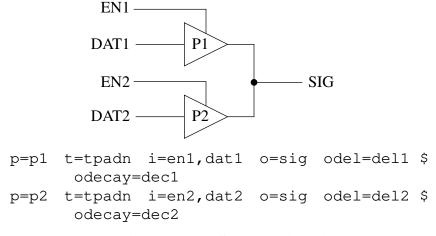

| memspike 2.6-2, 2.6-10, 2.6-21                       | odel, output-delay (SNL keyword) 2.7-9, B-6           |

| meta-words, for primary signals 2.4-4, C-1           | B-16                                                  |

| <b>minimum</b> timing 2.2-6, 2.6-33, C-41            | odom, output-dominance (SNL keyword)                  |

| min-max delays, and tolerance B-3, B-4               | 2.7-22, B-16                                          |

| modifying decays 2.6-34, C-61                        | odrive, output-drive (SNL keyword) 2.7-24             |

| mux SIMIC primitive A-35                             | B-16                                                  |

| •                                                    | ofall, output-fall (SNL keyword) 2.7-11, B-16         |

|                                                      | offsetting (skewing) stimuli 2.3-5                    |

| n (stimulus symbol) 2.3-12                           | ofilter, output-filter (SNL keyword) 2.7-21           |

| name (stimulus) 2.3-3, C-25                          | B-16                                                  |

| name-based filtering 52 – 56, C-31                   | ohdrive, output-hdrive (SNL keyword)                  |

| name-based <b>LIST</b> filtering 2.9-3 – 2.9-6, C-43 | 2.7-24, B-16                                          |

| names (character set) 1.2-3                          | oldrive, output-ldrive (SNL keyword) 2.7-24           |

| naming faults 9 – 10                                 | B-16                                                  |

| nand SIMIC primitive A-36                            | oliberal, output-liberal (SNL keyword)                |

| nandl SIMIC primitive A-37                           | 2.7-21, B-17                                          |

| NE enable mask 2.8-2, 2.8-5, C-27                    | olod, output-loads (SNL keyword) 2.2-7                |

| near filter 2.5-2                                    | 2.7-11, B-17                                          |

| near hazard 2.6-2                                    | omitting output name 1.2-6                            |

| and X-propagation 2.5-2, 2.6-35, C-77                | one 1.2-4, 1.2-6                                      |

| defining window of 2.6-4, C-23                       | oonand SIMIC primitive A-40                           |

| near propagation 2.5-2                               | opad, output-pads (SNL keyword) B-17                  |

|                                                      |                                                       |

| history                                            | disabling oscillation check 2.6-5, C-24                 |

|----------------------------------------------------|---------------------------------------------------------|

| file 2.9-2, C-42                                   | unlimited print/write width 2.4-5, C-48,                |

| list 2.9-1, C-42                                   | C-75                                                    |

| prange 2.9-2, C-42                                 | infinite (SNL decay value) 2.7-15, 2.7-16,              |

| <b>pstep</b> 2.9-2, C-43                           | B-13, B-16                                              |

| string 2.9-4 – 2.9-6, C-43                         | inhibit command options 1.1-10                          |

| history file                                       | initiate simulation 1.1-7, C-63                         |

| dump interval 2.9-2, C-43                          | input high-impedance default 2.7-16                     |

| enabling generation 2.9-1, C-42                    | input list 1.2-4, 1.2-5                                 |

| general 2.9-1                                      | input stimuli 2.3-1, 2.3-16                             |

| name-based filtering 2.9-3 – 2.9-6, C-43           | instantiating macros 2.7-3                              |

| restricting active interval 2.9-2                  | int, integer2 (2's-complement format) 1.2-13,           |

| sequential 2.9-1                                   | 2.4-8, B-3, C-26                                        |

| specifying name 2.9-2, C-42                        | int1, integer1 (1's-complement format)                  |

| hold time checks                                   | 1.2-13, 2.4-8, B-3, C-26                                |

| <b>hold</b> (all hold checks) 2.6-5, 2.7-18, A-20, | <b>integer</b> (stimulus format) 2.3-4, 2.3-11, C-25    |

| A-22, A-24, A-26, A-31, A-33,                      | interval representation 2.6-6, 2.6-7                    |

| A-56, A-63                                         | intervals, and SIMIC output characters 2.6-7            |

| hold.d 2.6-4, 2.7-17, A-20, A-22, A-24,            | inv SIMIC primitive A-29                                |

| A-26                                               | ipad, input-pads (SNL keyword) B-15                     |

| <b>hold.j</b> 2.6-4, 2.7-17, A-31, A-33            |                                                         |

| hold.k 2.6-4, 2.7-17, A-31, A-33                   |                                                         |

| hold.nr 2.6-4, 2.7-17, A-20, A-22, A-24,           | <b>jkcf</b> ( <b>jkncf</b> ) SIMIC primitive A-30, A-31 |

| A-26, A-31, A-33, A-56, A-63                       | <b>jkncf</b> ( <b>jkcf</b> ) SIMIC primitive A-30, A-31 |

| hold.ns 2.6-4, 2.7-17, A-20, A-22, A-24,           | <b>jkpcf</b> SIMIC primitive A-32, A-33                 |

| A-26, A-31, A-33, A-56, A-63                       |                                                         |

| hyphen placeholder 1.2-12                          |                                                         |

|                                                    | keyword-field (command) 1.1-9                           |

|                                                    | keyword-field (SNL) 1.1-4, 1.2-1                        |

| i (stimulus symbol) 2.3-12                         |                                                         |

| i, inet, input-nets (SNL keyword) 1.2-5,           |                                                         |

| 1.2-11, B-15                                       | lastaddr (SNL keyword) A-48, A-50, A-52,                |

| i, ipin, input-pins (SNL keyword) 1.2-4,           | A-54, B-15                                              |

| 1.2-11, B-15                                       | leaving SIMIC 1.1-2, 1.1-8                              |

| ihiz, input-hiz (SNL keyword) 2.7-16, B-15         | lev, level (SIMIC level format) 1.2-13, 2.4-8,          |

| ilod, input-loads (SNL keyword) 2.7-11, B-15       | B-3, C-26                                               |

| implicit file extensions (see default file exten-  | <b>levels</b> (print/write) 2.4-8, C-47, C-74           |

| sions)                                             | liberal, spike control parameter 2.6-2, 2.7-20          |

| incremental sensitization analysis 23 – 24         | restoring original SNL value 2.6-37, C-78               |

| incremental simulation 2.6-41                      | run-time modification 2.6-37, C-78                      |

| incremental test generation 39 – 41, C-34, C-58    | line continuation 1.1-11                                |

| auto-numbered directories $23 - 24$ , $39 - 41$    | line width of report files 22, 36, C-33, C-58           |

| file 32, 33, C-34                                  | <b>list</b> keyword, and valid names 2.4-4, C-1         |

| inertial filtering 2.5-3, 2.7-19                   | listing file 2.2-4                                      |

| infinite (run command value)                       | listing file options 2.2-5                              |

| decay value 2.6-35, C-61                           | load SIMIC primitive A-34                               |

|                                                  | implicit (default) 2.1-2, C-23                      |

|--------------------------------------------------|-----------------------------------------------------|

|                                                  | spanning directories 2.1-3                          |

| fall (SNL keyword) 2.7-9, B-5                    | filter, spike control parameter 2.6-2, 2.7-20       |

| fault                                            | restoring original SNL value 2.6-37, C-78           |

| coverage 25                                      | run-time modification 2.6-37, C-78                  |

| deferred 65                                      | filtering faults 52 – 56, C-31                      |

| filtering 52 – 56, C-31                          | finding all signals at X 2.6-29, C-45               |

| grading 25                                       | finding all signals at Z 2.6-29, C-45               |

| names 9 – 10                                     | fixed-point number 2.7-7, B-4                       |

| report files 32, 34 – 36, C-32                   | floating (drive strength) 2.7-24, B-13, B-14,       |

| sampling 57 – 61, C-36                           | B-16                                                |

| selection 25 – 27, C-30                          | floating (stimulus strength) 2.3-4, 2.3-9, C-25     |

| storage 65, C-37                                 | floating-point number 2.7-7, B-4                    |

| undetectable 9                                   | forcing signal states 2.6-30 – 2.6-32, C-19,        |

| fault                                            | C-60                                                |

| concurrent 66, C-37                              | <b>format statements</b> 1.2-11 – 1.2-13, B-6 – B-8 |

| confidence 59, C-36                              | formatting (print/write) 1.1-7                      |

| <b>directory</b> 32, 40, 41, C-35, C-36          | freeing forced values 2.6-31                        |

| <b>expand</b> 36, C-33                           | fundamental mode (patterns) 1.1-7, 2.3-1            |

| include 56, C-37                                 | randamentar mode (patterns) 1.1 7, 2.3 1            |

| input 26, C-30                                   |                                                     |

| Ifile 26, 40, C-30                               | get                                                 |

| list 25, C-30                                    | <b>afile</b> 2.2-6, C-41                            |

| output 26, C-30                                  | file 2.2-2, C-39                                    |

| <b>pdetect</b> 44 – 50, C-33, C-34               | lfile 2.1-2, 2.2-5, C-40                            |

| report 34 – 36, 43, 67, C-32, C-33, C-38         | report 2.2-5, C-40                                  |

| sample 57, 58, C-36                              | rfile 2.2-6, C-40                                   |

| <b>sfile</b> 33, 40, C-34                        | sfile 2.2-4, C-40                                   |

| storage 65, C-37                                 | stop 2.2-3, C-39                                    |

| string 53 – 56, C-31                             | timing 2.2-6, 2.6-33, C-41                          |

| tritest 57, C-37                                 | type 1.1-6, 2.2-2, 2.7-4, C-39                      |

|                                                  |                                                     |

| ufile 62, C-34<br>fault sample                   | glitch 2.5-3                                        |

| ±                                                | good-logic simulation 2.5-2<br>grade, fault 25      |

| from collapsed set 58, C-36                      |                                                     |

| from complete set 58, C-36                       | upper bound on 16                                   |

| specifying percentage 57, 58, C-36               |                                                     |

| fault simulation 2.5-2                           | have have decimal (amove format) 1.2.12. D.2        |

| fault-free simulation 2.5-2                      | hex, hexadecimal (array format) 1.2-13, B-3         |

| faults simulated per pass, specifying 66, C-37   | hex, hexadecimal (output format) 2.4-8, C-26        |

| FILE 2.6-18                                      | hexadecimal (stimulus format) 2.3-4, 2.3-11,        |

| file extension, default (see default file exten- | C-25                                                |

| sions)                                           | hierarchical names 2.7-4                            |

| file extension, specifying 2.1-1                 | hierarchical precedence, SNL 2.7-25 – 2.7-27        |

| file names                                       | hierarchical stimuli 2.3-8                          |

| constructing 2.1-1, 2.1-2                        | hierarchy (SNL macros) 2.7-1                        |

| explicit 2.1-3                                   | high-impedance, sensing at tester 57, C-37          |

| <b>p</b> <name> 1.1-6, 2.3-3, C-25</name>           | C-24                                                  |

|-----------------------------------------------------|-------------------------------------------------------|

| period 2.8-1, C-26                                  | detected faults, reporting 34, 35, C-32               |

| <b>pulse</b> 2.6-2, C-24                            | detecting high-impedance outputs 57, C-37             |

| rdepth 2.6-6, C-24                                  | detection, definition of 8                            |

| s <name> 2.8-8, C-28</name>                         | directory                                             |

| stability 2.5-4, C-24                               | auto-numbered $23 - 24$ , $39 - 41$ , C-35,           |

| t <name> 2.8-3, C-27</name>                         | C-58                                                  |

| v <name> 2.4-8, C-26</name>                         | fault output 32, C-35                                 |

| w <name> 2.3-3, C-25</name>                         | sensitization analysis output C-58                    |

| xaddress A-48, A-50, A-52, A-54, C-24               | disabling X-propagation 2.6-35, C-77                  |

| defining stimuli                                    | disconnect option, tester interface file 2.8-10,      |

| absolute positioning 2.3-15                         | C-64                                                  |

| default duration 2.3-3, 2.3-14, C-25                | dl (dpl) SIMIC primitive A-23, A-24                   |

| default format 2.3-3, C-25                          | dncf SIMIC primitive A-21, A-22                       |

| default strength 2.3-3, 2.3-9, C-25                 | dnl SIMIC primitive A-25, A-26                        |

| explicit duration 2.3-15                            | do loops (stimuli) 2.3-7                              |

| hierarchical 2.3-8                                  | double quotes 1.2-3, 2.1-2                            |

| name 2.3-3, C-25                                    | <b>dpcf</b> ( <b>dcf</b> ) SIMIC primitive A-19, A-20 |

| positioning precedence 2.3-16                       | dpl (dl) SIMIC primitive A-23, A-24                   |

| radix escapes 2.3-12                                | drive parameters, modifying 2.6-39                    |

| repetitive 2.3-7                                    | drive strength, specifying in SNL 2.7-24              |

| stimulus positioning 2.3-14 – 2.3-16                | drive values, tester 2.8-2                            |

| width 2.3-3, C-25                                   | driving (default stimulus strength) 2.3-4,            |

| delay (SNL keyword) 2.7-9, B-5                      | 2.3-9, C-25                                           |

| delay names                                         | driving (drive strength) 2.7-24, B-13, B-14,          |

| global 2.7-9, B-5                                   | B-16                                                  |

| referencing 2.7-9, B-6                              | dump format 2.4-3, 2.6-29, C-44, C-46, C-74           |

| uniqueness 2.7-10                                   | dynamic (ON ideal switches) 2.5-4, C-23               |

| delay specification                                 | dynamic delays (ON ideal switches) 2.5-4,             |

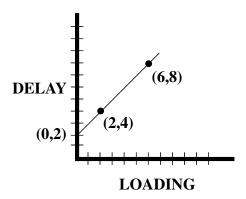

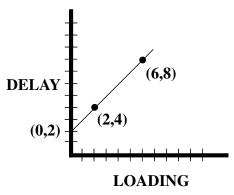

| intercept-slope form 2.7-8, B-5                     | C-23                                                  |

| two-point form 2.7-8, B-5                           | dynamic logic, and charge decay 2.5-3                 |

| typ;min;max 2.7-9, B-6                              |                                                       |

| <b>delay statement</b> 1.2-1, 2.7-7 – 2.7-10, B-4 – |                                                       |

| B-6                                                 | enabling X-propagation 2.6-35, C-77                   |

| delay table (see !delay) 2.7-7                      | entering SIMIC 1.1-1                                  |

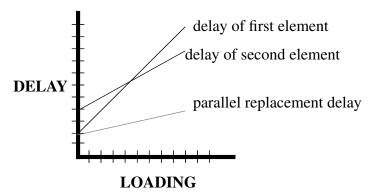

| delay vs. loading 2.2-1, 2.7-7, 2.7-8, B-5          | equivalent faults                                     |

| automatic computation 2.7-12, B-6                   | definition of 8, 9                                    |

| delays                                              | reporting 17, 18, 19, 20, 34, C-32, C-57              |

| and paralleled elements 2.7-13                      | estimating physical circuit size 2.7-29               |

| default (0) 2.7-9, B-4                              | execute file 1.1-12, C-29                             |

| global (see <b>delay statement</b> )                | exit on end-of-file 1.1-2                             |

| local 2.7-11                                        | exiting SIMIC 1.1-2, 1.1-8                            |

| resultant 2.7-12                                    | exnor SIMIC primitive A-27                            |

| run-time modification 2.6-15, 2.6-33,               | exor SIMIC primitive A-28                             |

| 2.6-34, 2.7-14, C-61                                | explicit duration (stimuli) 2.3-15                    |

| depth and strength correspondences 2.6-5.           |                                                       |

| cancelling forced values 2.6-31                    | in box score 59                                   |

|----------------------------------------------------|---------------------------------------------------|

| case sensitivity 1.1-1, 2.1-2, 2.2-3               | confidence level, specifying 58, C-36             |

| causality message, format 2.6-25                   | continuation 1.1-11, 1.2-2                        |

| causality, in trace 2.6-12, 2.6-14, 2.6-25, C-66   | coverage, fault 25                                |

| change (SNL keyword) 2.7-9, B-5                    | upper bound on 16                                 |

| character set (print/write) 2.4-7                  | •                                                 |

| character set, and names 1.2-3                     |                                                   |

| checkpoints, creating 2.6-40, C-55                 | dcf (dpcf) SIMIC primitive A-19, A-20             |

| checkpoints, restoring 2.6-39, C-53, C-54          | debugging commands 2.6-1 – 2.6-41                 |

| clamp                                              | decays                                            |

| \$\bar{boolean-equations}\$ 2.7-29                 | and stability 2.5-3, C-24                         |

| and A-43, A-46, C-20                               | default (0) 2.7-15                                |

| bitmap A-43, A-44, A-46, C-20                      | in SNL 2.7-15                                     |

| boolean A-13, C-21                                 | querying values 2.6-34, C-50                      |

| data A-48, A-50, A-52, A-54, C-21                  | run-time modification 2.6-34, 2.7-16, C-61        |

| enable A-43, C-21                                  | default delay tolerance B-3, B-4                  |

| hiz 2.6-30, C-19                                   | default duration (stimuli) 2.3-3, 2.3-7, 2.3-14,  |

| <b>list</b> (with <b>no</b> prefix) 2.6-31         | C-25                                              |

| one 2.6-30, C-19                                   | default duration, and primitive values 2.3-9      |

| or A-44, A-46, C-20                                | default file extensions                           |

| part A-13, A-43, A-44, A-46, A-48, A-50,           | ann (backannotate loading) 2.2-7, C-41            |

| A-52, A-54, C-20, C-21                             | brk (break messages) 2.6-19, C-18                 |

| tnum 2.6-30, C-19                                  | hig (general history) 2.9-1, C-42                 |

| type A-13, C-21                                    | his (sequential history) 2.9-1, C-42              |

| x 2.6-30, C-19                                     | <b>lst</b> (listing) 2.1-2, 2.2-5, C-40           |

| <b>zero</b> 2.6-30, C-19                           | <b>net</b> (network descr.) 1.1-6, 2.2-2, C-39    |

| clamp, compared to set 2.6-30                      | rnt (compiled network) 2.2-4, C-40                |

| clamp, overriding set 2.6-31                       | <b>run</b> (run command) 1.1-12, C-29             |

| collapsed fault set 8                              | sav (save, restore) 2.6-40, C-53, C-55            |

| collapsed faults, restricting reports to 36, C-32  | <b>tgn</b> (tester interface) 2.6-35, 2.8-9, C-64 |

| combinational hazard (see near, pulse, spike       | <b>trc</b> (trace) 2.6-25, C-67                   |

| hazards)                                           | wrn (warn) 2.1-3, 2.6-24, C-72                    |

| combinational timing hazards 2.6-2                 | wrt (write) 2.1-2, 2.4-2, C-73                    |

| command line options                               | default filename 1.1-6, 2.1-2                     |

| run file 1.1-12                                    | default format (stimuli) 2.3-3, C-25              |

| <b>-s</b> 1.1-1, 2.1-2, 2.2-3                      | default format, and primitive values 2.3-9        |

| command syntax 1.1-9 – 1.1-11                      | default point strobe 2.8-9                        |

| command verb 1.1-9                                 | default strength (stimuli) 2.3-3, 2.3-9, C-25     |

| comments (run commands) C-1                        | default strength, and primitive values 2.3-9      |

| comp, composition (SNL keyword) B-15               | default time-set 2.8-7                            |

| compilation (see <b>get</b> ) 1.1-6, 2.2-1 – 2.2-5 | deferred faults 65                                |

| compilation, saving 2.2-4, C-40                    | define                                            |

| complete fault set 8                               | <b>btgdelay</b> 2.5-4, C-23                       |

| composition (SNL keyword) 2.7-29                   | file 1.1-6, 2.1-2, C-23                           |

| concurrency 65, 66, C-37                           | near 2.6-4, C-23                                  |

| confidence interval 58, C-36                       | oscillation 2.6-5, C-24                           |

| bchange, bus-change (SNL keyword) 2.7-11,                       | rise 2.6-19, C-14                            |

|-----------------------------------------------------------------|----------------------------------------------|

| B-13                                                            | <b>spike</b> 2.6-10, 2.6-21, C-15            |

| bdec, bus-decay (SNL keyword) 2.7-15, B-13                      | <b>strobe</b> 2.6-23, 2.8-8, C-16            |

| bdel, bus-delay (SNL keyword) 2.7-9, B-6,                       | term 2.6-19, C-17                            |

| B-13                                                            | tstep 2.6-23, C-17                           |

| <b>bdom, bus-dominance</b> (SNL keyword)                        | unstable 2.6-22, C-16                        |

| 2.7-22, B-13                                                    | <b>x</b> 2.6-20, C-14                        |

| bdrive, bus-drive (SNL keyword) 2.7-24,                         | break messages 2.6-12                        |

| B-13                                                            | directing 2.6-19, C-17                       |

| behavioral (SNL composition) 2.7-28, B-15                       | format 2.6-18                                |

| bfall, bus-fall (SNL keyword) 2.7-11, B-14                      | break, on                                    |

| <b>bfilter, bus-filter</b> (SNL keyword) 2.7-21, B-14           | periodic interval (test/time) 2.6-22, C-17   |

| bhdrive, bus-hdrive (SNL keyword) 2.7-24,                       | specific signal transition 2.6-19, C-13      |

| B-14                                                            | break/warn, on                               |

| binary (default stimulus format) 2.3-4, 2.3-11,                 | combination hazard C-14, C-69                |

| C-25                                                            | combinational hazard 2.6-21                  |

| blank lines 1.1-11, 1.2-2                                       | conflict (wire-tie) 2.6-20, C-16, C-71       |

| bldrive, bus-ldrive (SNL keyword) 2.7-24,                       | input change while unstable 2.6-22, C-16,    |

| B-14                                                            | C-70                                         |

| bliberal, bus-liberal (SNL keyword) 2.7-21,                     | oscillation 2.6-21, C-17, C-71               |

| B-14                                                            | restricting active interval 2.6-19           |

| <b>blod, bus-loads</b> (SNL keyword) 2.7-11, B-14               | sensitized X at memory element 2.6-20,       |

| <b>boolean</b> (SNL composition) 2.7-28, A-9, B-15              | C-14, C-68                                   |

| boolean (SNL keyword) A-9, A-12, B-14                           | specific signal transition C-68              |

| <b>boolean</b> , defining new primitive A-8 – A-14,             | spike 2.6-10                                 |

| C-21                                                            | spike at memory element 2.6-10               |

| box score                                                       | strobe error 2.6-23, C-16, C-70              |

| fault simulation 29, 30, 34, 35, 59, C-32                       | timing-check violation 2.6-22, C-16, C-70    |

| sensitization analysis 16, 17                                   | transition to X (unknown) 2.6-20, C-14,      |

| <b>bpad, bus-pads</b> (SNL keyword) B-14                        | C-69                                         |

| break                                                           | transition to Z (floating unknown) 2.6-20,   |

| <pre><timing-check-name> 2.6-22, C-16</timing-check-name></pre> | C-13                                         |

| <b>change</b> 2.6-19, C-13                                      | breakpoints, setting 2.6-18 - 2.6-23, C-13 - |

| <b>conflict</b> 2.6-21, C-16                                    | C-18                                         |

| decay 2.6-20, C-13                                              | brise, bus-rise (SNL keyword) 2.7-11, B-14   |

| <b>fall</b> 2.6-19, C-14                                        | <b>btgn</b> SIMIC primitive A-15, A-16       |

| file 2.6-19, C-17                                               | <b>btgp</b> SIMIC primitive A-15, A-16       |

| hazard 2.6-21, C-14                                             | btgrn SIMIC primitive A-17, A-18             |

| memlatch 2.6-20, C-14                                           | <b>btgrp</b> SIMIC primitive A-17, A-18      |

| memspike 2.6-10, 2.6-21, C-15                                   | by-order connection 1.2-6                    |

| near 2.6-21, C-15                                               | by-pin-name connection 1.2-6                 |

| oscillation 2.6-21, C-17                                        |                                              |

| part 2.6-22, C-16                                               |                                              |

| prange 2.6-19, C-13                                             | c, com, comment (SNL keyword) 1.2-16, B-1    |

| pstep 2.5-3, 2.6-22, C-17                                       | B-2, B-14                                    |

| <b>pulse</b> 2.6-21, C-15                                       | cancel command options 1.1-10                |

|                                                                 |                                              |

# **Index**

- (skip **!format** field) 1.2-12, B-7

!behavioral section 1.2-2 !delay section 1.2-2, 2.7-7 – 2.7-10, B-1, B-4 – B-6 !delay section, multiple files 2.7-10 !documentation section 1.2-2, 1.2-17, B-1,

**!format** statement 1.2-2, 1.2-11, 1.2-12, B-7 **!include** statement 1.2-2, 2.2-3, B-8 maximum depth B-8

**!logical** section 1.2-2, 1.2-4 – 1.2-14, B-8 – B-18

# (print/write formatting) 2.4-3, C-46, C-73 \$ (line continuation) 1.1-11, 1.2-2

\$= (continuation comment) 1.1-11, 1.2-3, 1.2-16, B-2

**% declare** statement 1.2-2, 1.2-13, 2.4-8, 2.7-5, B-1, B-2 – B-4

**&alphanumeric** string filter option 2.9-5, 54, C-31, C-43

**&busins** (all applied primary busses) metaword 2.4-4, C-2

**&busses** (all primary busses) meta-word 2.4-4, C-2

**&inputs** (all primary inputs) meta-word 2.4-4, C-1

**&numeric** string filter option 2.9-4, 2.9-5, 53, 54, C-31, C-43

**&outputs** (all primary outputs) meta-word 2.4-4, C-1

\* (print/write formatting) 1.1-7, 2.4-3, C-46, C-73

\* delimiter for CLAMPing **pla** A-43, A-44, C-20

\* in signal header 2.4-9

\* restore filter and liberal SNL values 2.6-37, C-78

\* restore last stable state 2.6-40, C-53

\* string specification delimiter 2.9-6, 55, C-31

\* suppress timing marks 2.8-5

: (keyword form) 1.1-9

>>: prompt 1.1-2

? value for restore tnum 2.6-41, C-53

?check part 2.6-37, C-50

?decay list 2.6-34, C-50

?define 2.5-1, C-50

?delay list 2.6-32, C-50

?drive list 2.6-39

?loading list 2.6-35, C-50

?print 2.4-9, C-51

?write 2.4-9, C-51

a, apin, aux-pins (SNL keyword) B-13

aanor SIMIC primitive A-6

abbreviation (commands) 1.1-11, C-3 – C-5

abort limit (compilation) 2.2-3, C-39

absolute positioning (stimuli) 2.3-15

abstraction, levels of 2.7-28

adding net loading 2.2-6, C-41

aliases 2.4-4, 2.4-8, C-2, C-26

all listing file option 2.2-5, C-40

all, disconnect option 2.8-10, C-64

and SIMIC primitive A-7

annotation (SNL) 1.2-15 – 1.2-17, B-1, B-2

apad, aux-pads (SNL keyword) B-13

apply

begin 2.3-5, 2.8-1, 2.8-7, 2.8-9, C-10, C-11, C-12

list 2.3-5, 2.8-7, 2.8-8, 2.8-9, C-10, C-11

patterns 1.1-7, 2.3-5, C-10

period 2.8-1, C-12

timing 2.8-7, 2.8-8, 2.8-9, C-11

applying stimuli 2.3-5, C-10

overriding previous applies 2.3-6

applying time-sets to inputs 2.8-7, C-11

array range 1.2-13, B-2

assigning strobes to outputs 2.8-8, 2.8-9, C-11

attention interrupt 1.1-2

auto-numbered directories 39 – 41, C-35, C-58

**b, bnet, bus-nets** (SNL keyword) B-13 **b, bpin, bus-pins** (SNL keyword) B-13 backannotating loading 2.2-6, C-41 batch operation 1.1-13

while the command:

NO XPROPAGATE PARTS: <timing-check>: disables X-propagation for the specified timing checks for all parts. Different timing checks may be specified in the same command.

For example, assuming part **f1** is a DCF primitive, the command:

NO XPROPAGATE PART=f1 HOLD: SETUP.NR: would disable X-propagation for all hold-time violations and for setup-time violations between the **NR** and **CLK** pins at this flip-flop.

Subsequently, X-propagation can be re-enabled with the same commands, except the **NO** prefix would be omitted. For example:

XPROPAGATE PART=f1 HOLD: SETUP.NR: re-enables X-propagation for all hold-time violations and for setup-time violations between the NR and CLK pins at flip-flop f1 of the previous example.

### **Modifying Spike Control Parameters**

The **liberal** and **filter** spike control parameters can be modified independently with the **XPROPAGATE** run command. The commands:

```

XPROPAGATE FILTER=<filt_lib> LIST=<signals> XPROPAGATE LIBERAL=<filt_lib> LIST=<signals> change the filter and liberal parameters, respectively, to the value <filt_lib> for the selected signals in <signals>. The commands:

```

```

XPROPAGATE FILTER=<filt_lib> LIST:

XPROPAGATE LIBERAL=<filt lib> LIST:

```

change the **filter** and **liberal** parameters, respectively, for all signals.

The *filt\_lib>* value is a percentage from 0 to 100, and is specified as an integer, optionally followed by a percentage sign (e.g. 50 or 50%). For example,

```

XPROPAGATE FILTER=20% LIST=abc, def sets the filter spike control parameter of signals abc and def to 20%.

```

An asterisk (\*) may be also be specified for *filt\_lib>* to restore the spike control parameters to their original values (in the SNL description). For example:

```

XPROPAGATE LIBERAL=* FILTER=* LIST: would reset all FILTER and LIBERAL parameters to their original values.

```

# **Run Command: XPROPAGATE (XP)**

### **Function**

The **XPROPAGATE** command is used to globally enable or disable X-pulse creation/propagation for **spike hazards** and **near hazards**.

The **XPROPAGATE** command is used to selectively enable or disable X-pulse creation/propagation for timing check violations at SIMIC D latches and edge-triggered flip-flop primitives.

The **XPROPAGATE** command is used to selectively modify the **filter** and **liberal** spike control parameters.

## **Usage**

SIMIC, by default, propagates an X whenever a spike, or part timing violation (setup, hold, or pulse-width) occurs. X-propagation is controlled by the **XPROPAGATE** command.

## Globally Enabling And Disabling X-Propagation For Hazards

The **SPIKE** keyword option globally controls whether X-propagation is performed for spike hazards. The command:

NO XPROPAGATE SPIKE:

globally disables X-propagation for spike hazards, while the command:

XPROPAGATE SPIKE:

globally re-enables it.

The NEAR keyword option globally controls whether X-propagation performed for near hazards. The command:

XPROPAGATE NEAR:

enables X-propagation for near hazards, while the command:

NO XPROPAGATE NEAR:

disables it.

By default, X-propagation is disabled for near hazards.

## **Controlling X-Propagation For Functional Timing Violations**

The **PART** keyword option, combined with individual timing check specifications, allow X-propagation for timing check violations to be controlled on a per-instance, per-check basis. The command:

NO XPROPAGATE PARTS=rarts\_ff> <timing-check>:

disables X-propagation for the specified timing check violations and parts,

The **HEADER** keyword option controls whether the simulation header, consisting of the simulation options and signal names, be output prior to the tabular simulation values. By default, the header is enabled. The command:

NO WRITE HEADER:

disables the header output, and the command:

WRITE HEADER:

enables it.

When waveform stimuli are used, the test number field of the simulation output can be optionally suppressed with the **TNUM** keyword option. By default, this field is present in every record. The command:

NO WRITE TNUM:

suppresses the test field. Each output line will contain the time, followed by a colon, followed by the requested signal values.

The test field can be restored with the command:

WRITE TNUM:

will cause an output to occur every *<integer>* simulation time-units. If the time-step specification is preceded by a plus ("+") sign, output will continue regardless of circuit stability. For example:

WRITE TSTEP=+100

produces output every 100 time-units, even when the circuit state is stable.

The **NO** prefix can be used to disable time-periodic output:

NO WRITE TSTEP:

The **BEGIN** keyword option may be used to skew (offset) the first **TSTEP** output. This command has the form:

WRITE BEGIN=<integer>

where *<integer>* specifies the time offset to the first output.

To remove the offset, specify a value of 0:

WRITE BEGIN=0

### **Requesting Output Based On Activity**

The **CHANGE** keyword option specifies that output be triggered by activity at monitored signals. The command form is:

WRITE CHANGE=<signals>

where *<signals>* is a subset of the signals currently being monitored with the **WRITE** command (other signals are ignored). This command specifies that output should occur whenever any of the specified signals changes state.

The command:

WRITE CHANGE:

will trigger write output when any of the monitored signals changes state.

Subsequently, the command:

NO WRITE CHANGE=<signals>

would inhibit the specified signals in *<signals>* from functioning as triggers, while:

NO WRITE CHANGE:

would disable all activity-based output.

#### **Header And Tabular Format Control**

SIMIC, by default, limits each output line to 80 columns. The **EXPAND** keyword option can be used to modify output line width. The command form:

WRITE EXPAND:

expands output line width to 132 columns, while the command form:

WRITE EXPAND=INFINITE

allows arbitrary output line width.

The second form of the **LIST** keyword:

```

WRITE LIST:

```

specifies that the values of *all* signals be reported in "dump" format; groups of five values ordered alphabetically, according to the **symbol** section of the listing file.

The **WRITE** command's **LIST** keyword is "sticky"; any signal specified will continue to be reported until explicitly removed. Removing signals from the list is accomplished with the **NO** prefix. For example:

```

NO WRITE LIST=a, b

```

removes signals **a** and **b** from the list of reported signals. The format options "\*" and "#" are not specified with the **NO** prefix. The command:

```

NO WRITE LIST:

```

removes all signals, thereby terminating **WRITE** output.

#### **Suppressing Signal Strength**

By default, a 15-character set is used to represent combined level and strength information. Optionally, output can be restricted to a 4-character set representing levels; **0**, **1**, **X**, and **Z** (although **Z** represents the combination of unknown level at floating strength). The **VALUES** keyword option is used to select value representation. The command:

```

WRITE VALUES=LEVELS

```

selects the 4-character representation, while the command:

```

WRITE VALUES=STRENGTHS

```

restores the 15-character default representation.

#### **Requesting Output At Stable Points**

The default **WRITE** operation is to output the requested simulation values each time the circuit becomes stable. The **PSTEP** (**PS**) keyword option can be used to control frequency of this output, or inhibit it. The command:

```

WRITE PSTEP=<integer>

```

changes this interval. For example:

```

WRITE PSTEP=5

```

specifies that output occur every fifth stable point.

Output based on attaining a stable state can be disabled with the **NO** command prefix:

```

NO WRITE PSTEP:

```

#### **Requesting Time-Periodic Output**

Output can be requested at specified time intervals using the **TSTEP** keyword. The command:

```

WRITE TSTEP=<integer>

```

# **Run Command: WRITE (WR)**

#### **Function**

The **WRITE** command is used to report selected signal values in a tabular format during simulation. Output is directed to a file.

# Usage

The **WRITE** command is described in Chapter 2.4.

The **WRITE** command can be restricted to a specified interval of tests, for patterns, or time, for waveforms, with the **PRANGE** keyword option:

WRITE PRANGE=range spec>

### **Specifying The File Name For The WRITE File**

By default, the extension of the file created by the **WRITE** command is **wrt**, and its name is the default name specified by the **DEFINE FILE** command. The **FILE** keyword can be used to explicitly specify this file's name:

WRITE FILE=<file name>

where *file name* is the name of the file to be written to.

#### **Specifying Signals and Format**

The **LIST** keyword is used to select signals and format the output: The command form for this selection is:

WRITE LIST=<signals and format>

where *<signals and format>* has the form of a *<signals>* specification, possibly augmented with formatting options. These options are:

- 1. Inserting one or more blank vertical columns between signals. This is accomplished by entering an asterisk (\*) for each blank column.

- 2. Forcing a new row in the table. This is accomplished by entering a pound sign (#) at the desired point.

Commas or whitespace are optional before or after \* or #.

For example:

```

WRITE LIST=u, v, *w**x#y

```

will cause the simulation output to consist of the value of signal  $\mathbf{u}$ , followed by the value of  $\mathbf{v}$ , followed by a blank column, followed by the value of  $\mathbf{w}$ , followed by two blank columns, followed by the value of  $\mathbf{x}$ . The value of signal  $\mathbf{y}$  will be output at the first position of the next line.

specifies a file with the default file name (see **DEFINE FILE**). If the second form is used, or if no file extension is specified in the first form, the file's default extension is **wrn**.

Regardless of how they were enabled, warn messages to a file are disabled with the command:

NO WARN FILE:

#### Warn On The Occurrence Of Wire-tie Conflicts

The **CONFLICT** keyword specifies a wire-tie conflict. The command:

```

WARN CONFLICT=<signals>

```

triggers a warning when a wire-tie conflict occurs at any of the specified signals, while the command:

```

WARN CONFLICT:

```

triggers a warning when any wire-tie conflict occurs.